(19) 日本国特許庁(JP)

## (12) 公開特許公報(A)

(11) 特許出願公開番号

特開2007-159991

(P2007-159991A)

(43) 公開日 平成19年6月28日(2007.6.28)

(51) Int.CI.

**A61B 1/04** (2006.01)

**G02B 23/24** (2006.01)

**HO4N 7/18** (2006.01)

F 1

A 61 B 1/04

G 02 B 23/24

H 04 N 7/18

3 7 2

A

M

テーマコード(参考)

2 H 04 0

4 C 06 1

5 C 05 4

審査請求 未請求 請求項の数 5 O L (全 16 頁)

(21) 出願番号

特願2005-363695 (P2005-363695)

(22) 出願日

平成17年12月16日 (2005.12.16)

(71) 出願人

304050923

オリンパスメディカルシステムズ株式会社

東京都渋谷区幡ヶ谷2丁目43番2号

(74) 代理人

100076233

弁理士 伊藤 進

(72) 発明者

高橋 和正

東京都渋谷区幡ヶ谷2丁目43番2号 オ

リンパスメディカルシステムズ株式会社内

Fターム(参考) 2H040 CA04 CA11 CA23 GA02 GA06

GA11

4C061 AA00 BB01 CC06 DD00 JJ15

LL02 NN01 NN05 QQ02 SS05

5C054 CC07 EA03 EC06 HA12

(54) 【発明の名称】内視鏡用信号処理装置

## (57) 【要約】

【課題】 低位相雑音特性に設定した状態で、周波数引込を簡単な構成で行うことを可能とするPLL回路を用いた内視鏡用信号処理装置を提供する。

【解決手段】 CCD駆動回路17からCCD15を経て、リファレンスクロックR-CLKがPLL回路27に入力されるのをR-ゲート26により開閉する。又、CCD15の空画素の読み出しとなる位相調整期間に位相比較器28の動作をイネーブルにする間欠動作制御信号\ENの開始タイミングを、遅延回路34により可変クロックV-CLKを遅延してこの可変クロックV-CLKと同期するようにタイミング調整し、ラッチ回路33を経て位相比較器28に印加する。そして、R-ゲート26を閉から開にすることにより、低位相雑音特性に設定した状態で、周波数引込を簡単な構成で行う。

【選択図】 図1

**【特許請求の範囲】****【請求項 1】**

着脱自在に接続される内視鏡に内蔵された撮像素子から出力される基準クロックに対し、電圧制御発振回路で発生した可変クロックを位相比較器で位相比較するフェーズロックドリープ回路を用いて、前記基準クロックに位相同期した可変クロックを生成する信号処理を行う内視鏡用信号処理装置において、

前記フェーズロックドリープ回路を、間欠的な期間、動作状態に設定する動作制御信号を発生する動作制御信号発生手段と、

前記動作制御信号の出力開始時のタイミングを、前記可変クロックの出力タイミングと少なくとも前記可変クロックの周期よりも短い所定時間内で同期させる同期タイミング設定手段と、10

前記基準クロックの前記フェーズロックドリープ回路への入力の開閉を行うゲート手段と、

を具備することを特徴とする内視鏡用信号処理装置。

**【請求項 2】**

さらに前記可変クロックが前記基準クロックに位相同期している状態か否かを検出する同期検出手段を有することを特徴とする請求項 1 に記載の内視鏡用信号処理装置。

**【請求項 3】**

前記可変クロックの周期を  $T$  とした場合、前記可変クロックの出力タイミングから  $T / 4 \sim T / 2$  程度以内に前記動作制御信号の出力開始時のタイミングとなるように前記所定時間が設定されることを特徴とする請求項 1 に記載の内視鏡用信号処理装置。20

**【請求項 4】**

前記同期検出手段は、前記可変クロックが前記基準クロックに位相同期していない時間が、所定時間を越えたか否かをモニタし、前記所定時間を越えた場合には、前記ゲート手段を一旦閉にした後、開にすることを特徴とする請求項 2 に記載の内視鏡用信号処理装置。。

**【請求項 5】**

さらに前記内視鏡に内蔵された撮像素子の種別の情報により、前記フェーズロックドリープ回路を構成する分周回路の分周比を制御することを特徴とする請求項 1 に記載の内視鏡用信号処理装置。30

**【発明の詳細な説明】****【技術分野】****【0001】**

本発明は、高画素の撮像素子を搭載した内視鏡にも対応可能な信号処理を行う内視鏡用信号処理装置に関する。

**【背景技術】****【0002】**

近年、撮像素子を搭載した内視鏡は医療用分野その他で広く用いられるようになった。また、内視鏡は、内視鏡検査する検査対象部位等に応じて挿入部の長さが異なる種類のものがある。この場合には、撮像素子から、撮像素子に対して内視鏡画像を生成する信号処理を行う信号処理装置までのケーブル長などが異なる。40

このようにケーブル長が異なると、撮像素子を駆動信号で駆動した場合、駆動信号の信号伝搬の遅延量が異なると共に、撮像素子から出力された出力信号が実際に信号処理装置に入力されるタイミングも異なる。

**【0003】**

このため、撮像素子からの出力信号中における実際の信号成分部分を抽出するためのサンプリングパルスの発生タイミングを、ケーブル長による遅延量に応じて適切に設定する調整作業が必要である。

このような調整作業を自動的に行えるように、フェーズロックドリープ回路 (PLL 回路) を用いた信号処理装置が、例えば特開平 6 - 86138 号公報に開示されている。50

この従来例においては、水平方向及び垂直方向に所定の画素数の画素が配列された撮像素子に駆動信号を印加して、撮像素子により光電変換された信号を読み出す場合、各水平方向の読み出し期間において、画素が存在しない空の画素の期間を位相調整期間としてその間欠的な期間においてゲート信号を発生してPLL回路を動作状態に設定して、撮像素子から出力される（基準クロックとしての）リセットパルスに位相同期したタイミング信号を生成するようにしている。

【特許文献1】特開平6-86138号公報

【発明の開示】

【発明が解決しようとする課題】

【0004】

しかしながら、最近においてはより高画素の内視鏡画像に対する要望があり、例えば3倍程度に画素数を増大した高画素の撮像素子に対して、従来例の構成を適用した場合、間欠的にPLL回路を動作させると共に、駆動信号の周波数が3倍程度になるため、周波数引込に必要なキャプチャレンジを確保しつつ、低位相雑音特性を実現することが非常に困難になる欠点があった。

このように高画素に対応して駆動信号の周波数を高くした場合には、その駆動信号の場合の撮像素子から出力される基準クロックとしてのリセットパルスに対して周波数引込と低位相雑音を両立させるためには、周波数引込（位相同期）させ易いタイミングでPLL回路を動作させることができが、各回路素子で許容されるばらつきを考慮すると、基準クロックの周波数が低い場合に比べるとそのようなタイミングに管理することが困難になる。

【0005】

この場合、PLL回路中のローパスフィルタ（LPF）のカットオフ周波数を下げれば、低雑音の小信号ループ特性を確保できるが、そのために周波数引込に要する時間が増大することになるため、ユーザに対する利便性を低下させてしまう。

このため、低位相雑音特性の条件に設定した状態で、（時間を増大させることなく）速やかに周波数引込ができるPLL回路を簡単な構成で実現できると非常に有益である。

【0006】

（発明の目的）

本発明は上述した点に鑑みてなされたもので、低位相雑音特性に設定した状態で、周波数引込を簡単な構成で行うことを可能とするPLL回路を用いた内視鏡用信号処理装置を提供することを目的とする。

【課題を解決するための手段】

【0007】

本発明は、着脱自在に接続される内視鏡に内蔵された撮像素子から出力される基準クロックに対して、電圧制御発振回路で発生した可変クロックを位相比較器で位相比較するフェーズロックドループ回路を用いて、前記基準クロックに位相同期した可変クロックを生成する信号処理を行う内視鏡用信号処理装置において、

前記フェーズロックドループ回路を、間欠的な期間、動作状態に設定する動作制御信号を発生する動作制御信号発生手段と、

前記動作制御信号の出力開始時のタイミングを、前記可変クロックの出力タイミングと少なくとも前記可変クロックの周期よりも短い所定時間内で同期させる同期タイミング設定手段と、

前記基準クロックの前記フェーズロックドループ回路への入力の開閉を行うゲート手段と、

を具備することを特徴とする。

上記構成によりフェーズロックドループ回路を、間欠的な期間、動作状態に設定する動作制御信号の出力開始時のタイミングを所定時間内で同期させるように同期タイミング設定をし、かつゲート手段により基準クロックの前記フェーズロックドループ回路への入力を閉から開にすることにより簡単な構成で周波数引込を行うようにしている。

10

20

30

40

50

## 【発明の効果】

## 【0008】

本発明によれば、低位相雑音特性に設定した状態で簡単な構成で周波数引込を行うことができる。

## 【発明を実施するための最良の形態】

## 【0009】

以下、図面を参照して本発明の実施例を説明する。

## 【実施例1】

## 【0010】

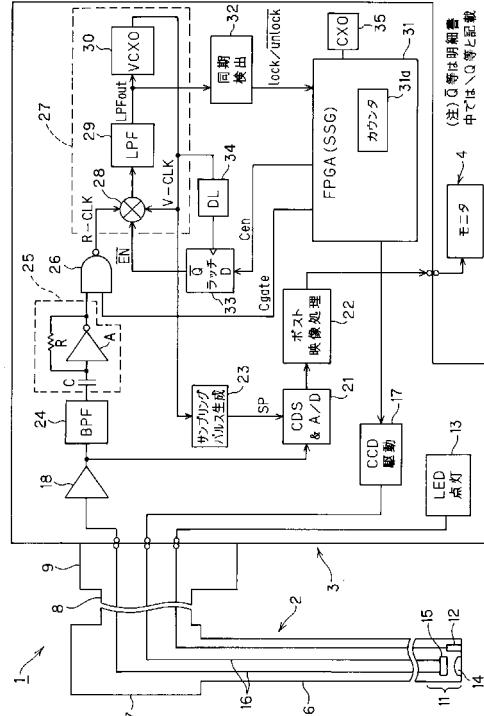

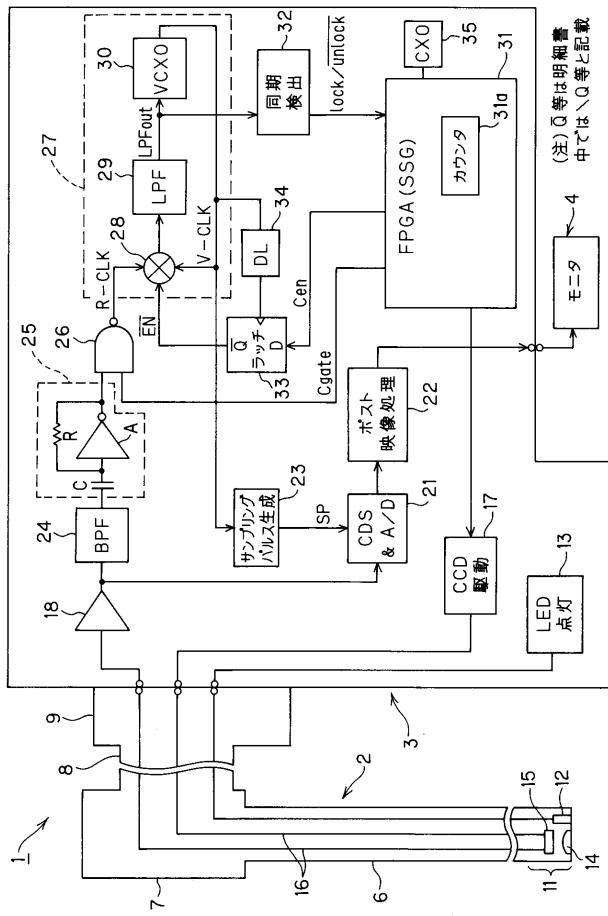

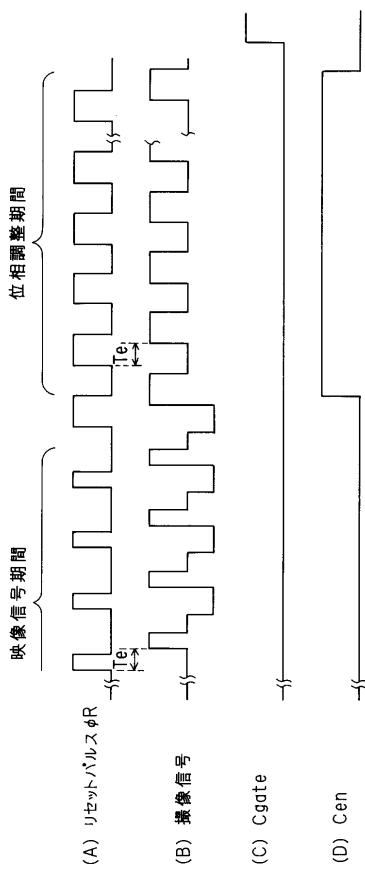

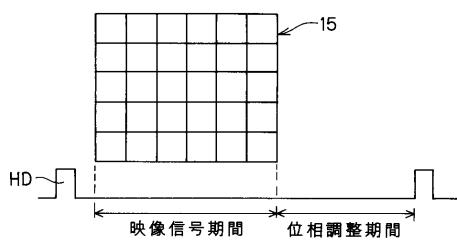

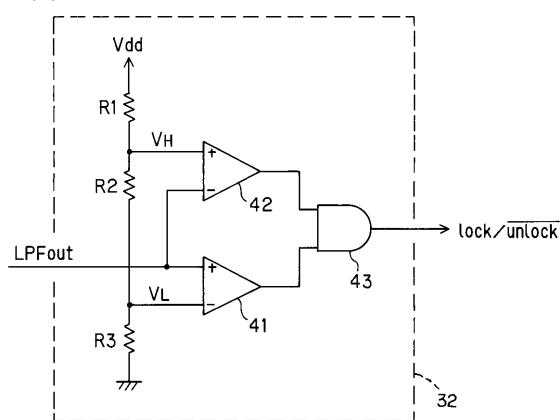

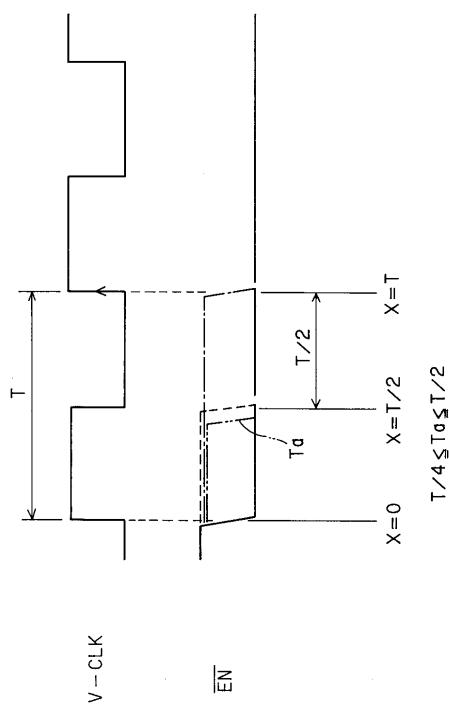

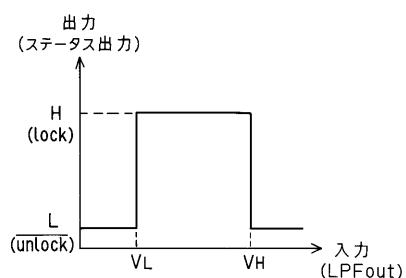

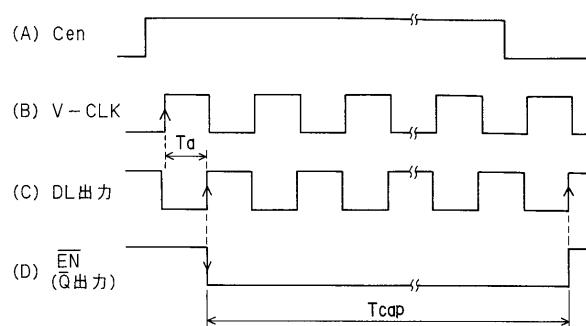

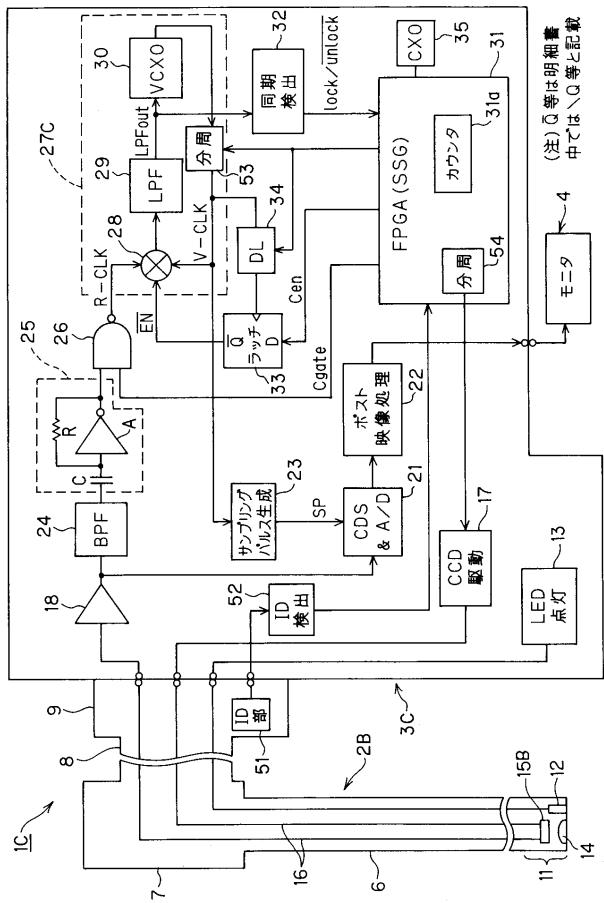

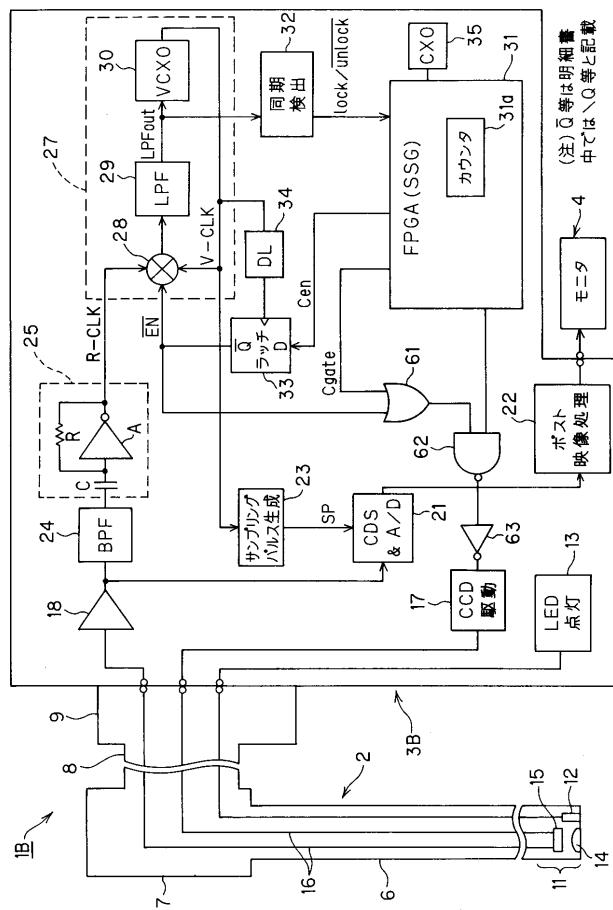

図1から図10は本発明の実施例1に係り、図1は本発明の実施例1を備えた内視鏡システムの全体構成を示し、図2は内視鏡を接続して駆動した場合におけるリセットパルス、撮像信号等のタイミングを示し、図3は映像信号期間と位相調整期間の説明図を示し、図4は同期検出回路の構成例を示し、図5は図4の動作説明図を示し、図6はPLL回路における可変クロックと、位相比較器を動作状態に設定する間欠動作用ゲート信号とを周波数引込させ易い所定のタイミングに同期させることの説明図を示す。

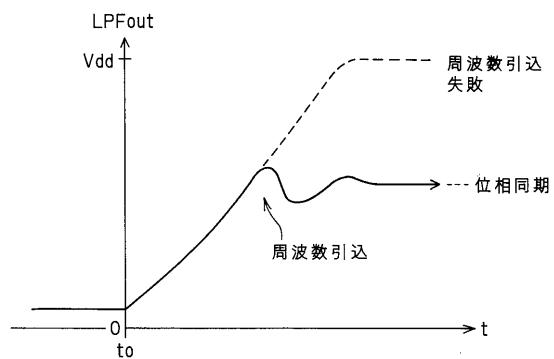

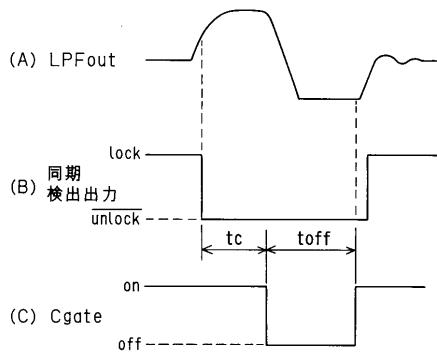

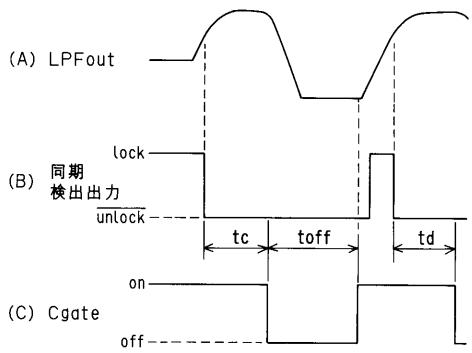

図7はPLL動作させた場合の各部の出力を示すタイミングチャートを示し、図8はゲート信号をoffからonにしてPLL回路を動作させた場合における周波数引込を行う様子を示し、図9は同期状態をモニタして、同期が外れた場合には一旦ゲート信号をoffにした後、onにして周波数引込を行う様子を示し、図10は図9の動作の場合においてさらに周波数引込に失敗した場合の動作例を示す。

## 【0011】

図1に示すように本発明の実施例1を備えた内視鏡システム1は、内視鏡検査を行うための電子内視鏡2と、この電子内視鏡2が着脱自在に接続され、電子内視鏡2に搭載された撮像素子に対する信号処理を行う内視鏡用信号処理装置としてのビデオプロセッサ3と、このビデオプロセッサ3から出力される映像信号が入力されることにより撮像素子で撮像された画像を内視鏡画像として表示するモニタ4とを有する。

電子内視鏡2は、体腔内等に挿入される細長の挿入部6と、この挿入部6の後端(基端)に形成された操作部7と、この操作部7から延出されたユニバーサルケーブル部8とを有し、このユニバーサルケーブル部8の後端に設けたコネクタ9はビデオプロセッサ3に着脱自在に接続される。

## 【0012】

挿入部6における先端に設けられた先端部11には、照明光を射出する照明窓が設けてあり、例えば白色LED12が取り付けてあり、ビデオプロセッサ3に設けたLED点灯回路13から駆動線を介してLED点灯用の電源が供給されることにより点灯して白色の照明光を射出する。

この照明窓に隣接して設けられた観察窓(撮像窓)には対物レンズ14が取り付けてあり、その結像位置には撮像素子として例えば電荷結合素子(CCDと略記)15が配置されている。

このCCD15は、挿入部6内部等を挿通された信号ケーブル16を介してビデオプロセッサ3内に設けたCCD駆動回路17とフロントエンドアンプ(FEAと略記)18とに接続される。

## 【0013】

そして、CCD駆動回路17から一定周期で出力されるリセットパルスR等を含むCCD駆動信号が信号ケーブル16(の駆動線を介して)CCD15に印加されることにより、CCD15は光電変換して蓄積した信号電荷を撮像信号(或いはCCD出力信号)として出力する。この撮像信号は、信号ケーブル16(の信号線を介して)FEA18に入力される。

なお、図1において、CCD15は、通常の画素数のものよりも3倍程度の画素数を有する高画素CCDであり、このために通常の画素数の場合の水平転送パルスやリセットパルスRの周波数(10MHz程度)に対して、本実施例では30MHz程度に高い周波

10

20

30

40

50

数に設定されている。また、図1では1つの電子内視鏡2が示してあるが、挿入部6の長さなど、ケーブル長が異なる電子内視鏡の場合にも、図1のビデオプロセッサ3は共通に対応できるようにPLL回路27を採用して信号処理系を形成している。

#### 【0014】

CCD駆動信号における例えりセットパルスRは、図2(A)に示すように図示しない水平転送信号等と同期して出力される。そして、図2(B)に示すように、例えりセットパルスRから時間Te遅延した撮像信号がFEA18に入力される。

また、この場合、左側に示す映像信号期間は、CCD15からそのCCD15における水平方向の画素数を読み出す期間であり、撮像信号の波形は、各画素における輝度情報に応じて変化する。これに対して、右側に示す位相調整期間は、CCD15における水平方向の画素分を読み出し終えた(或いは読み出す前の)輝度情報の無い無信号期間(空信号期間)を示す。この期間においてもリセットパルスRは図2(A)の通り印加され、その結果、図2(B)の通り、CCD15から出力信号が、PLL回路入力のための基準クロックとして出力される。

なお、図2では位相調整期間ではリセットパルスRを映像信号期間と分離し易いようにそのデューティを変えているが、これはこれらの期間を分離し易くするもので、位相調整に不可欠のものでない。

#### 【0015】

図2において、右側の位相調整期間の後に、次の水平方向の画素分を読み出す映像信号期間が続くことになる。

つまり、CCD15は図3に示すように水平方向及び垂直方向にそれぞれ所定数の画素が配列されている。この場合、水平同期信号(図3ではHDと略記)に同期してCCD駆動信号におけるリセットパルスRなどの印加により水平方向の画素数分が読み出される期間が映像信号期間となり、これに隣接する空読み出しの期間が位相調整期間となる。このようにして映像信号期間と位相調整期間とが繰り返される。

上記FEA18により増幅された撮像信号は、CDS&A/D回路21に入力され、CDS回路部分において相関二重サンプリング(CDS)処理により、撮像信号中における信号部分が抽出されてベースバンドの信号に変換された後、A/D回路部分でデジタル信号に変換される。このデジタル信号は、ポスト映像処理回路22に入力され、映像信号が生成され、モニタ4に出力される。

#### 【0016】

上記CDS回路部分には、サンプリングパルス生成回路23から後述するPLL回路27から出力される可変クロックVCLKに同期したサンプリングパルスSPが供給される。

このサンプリングパルスSPにより、CDS回路部分は撮像信号中における信号部分をサンプリングする。このサンプリングパルスは、図2(B)に示す撮像信号における(リセットパルス直後の)フィードスルー部と輝度情報部とをそれぞれサンプリングし、それらの差信号を抽出して、ベースバンドの信号を生成する。

#### 【0017】

また、FEA18により増幅された撮像信号は、位相調整期間におけるリセットパルスRを(基準クロックとなるリファレンスクロックとして)抽出するように帯域制限されたバンドパスフィルタ(BPF)24を通り、さらにリミッタアンプ25により波形整形される。

このリミッタアンプ25は、例え交流信号を通すコンデンサC、抵抗Rが入出力端間に接続された反転アンプAにより構成される。

このリミッタアンプ25により波形整形されたリセットパルスRの信号は、リファレンスクロックゲート(以下R-ゲートと略記)26を経てリファレンスクロックR-CLKとして、PLL回路27を構成する位相比較器28に入力される。このR-ゲート26は、例えNAND回路により構成されている。なお、R-ゲート26は、リファレンスクロックR-CLKのPLL回路27への入力の開閉を行うゲート手段を形成している。

10

20

30

40

50

## 【0018】

上記位相比較器28は、後述する間欠動作制御信号 $\setminus EN$ が”L”で印加されると、位相比較動作を行い、この間欠動作制御信号 $\setminus EN$ が”H”になると位相比較動作を停止する。

この位相比較器28は、R-ゲート26を経て入力されるリファレンスクロックR-CLKと、電圧制御発振器(VCXO)30が出力する可変クロックV-CLKとの位相比較を行い、その位相差に対応した信号をLPF29に出力する。

このLPF29は、位相比較器28の出力信号における低域成分の信号を、このLPF29の出力信号LPFoutとしてVCXO30に出力する。そして、このVCXO30は、その入力端に印加されるLPF29の出力信号LPFoutの電圧値に応じて(例えれば略比例して)その発振周波数が変化する可変クロックV-CLKを出力する。

10

## 【0019】

つまり、このVCXO30は、LPF29の出力信号LPFoutの電圧値に対応した周波数若しくは位相の可変クロックV-CLKを位相比較器28に出力すると共に、サンプリングパルス生成回路23にも出力する。

本実施例においては、PLL回路27は、ケーブル長が異なる場合においても、無調整で適切なタイミングでサンプリングパルスSPを生成するためのものであり、リファレンスクロックR-CLKの周波数は殆ど一定である(CCD15の画素数により決まる)ので、これに対応してVCXO30を周波数の安定性の良い水晶発振素子を用いて可変クロックV-CLKを生成するようにしている。

20

つまり、本実施例では、可変クロックV-CLKを、リファレンスクロックR-CLKの位相に位相同期させるためにPLL回路27を用いている(従って、リファレンスクロックR-CLKの周波数と可変クロックV-CLKとの周波数は、可変クロックV-CLKの周波数が変化する変化幅を考慮しても略等しいと見なすことができる)。

## 【0020】

なお、本実施例では、位相比較器28は、可変クロックV-CLKの立ち上がりエッジと、リファレンスクロックR-CLKの立ち上がりエッジとのタイミングずれ、つまり両クロックの出力タイミングの位相差を検出する。そして、位相比較器28は、その位相差に対応した信号をLPF29に出力する。

例えば、リファレンスクロックR-CLKの立ち上がりエッジのタイミングに対して可変クロックV-CLKの立ち上がりエッジのタイミングが進んでいると、その位相差に対応してLPF29の出力信号LPFoutの電圧値が下がり、可変クロックV-CLKの立ち上がりエッジのタイミングを遅らせるようにVCXO30の可変クロックV-CLKの発振周波数を低くする(その位相差を小さくするように位相を遅らせる)。

30

## 【0021】

これと逆の場合には、VCXO30の可変クロックV-CLKの発振周波数を高くする(その位相差を小さくするようにその位相を進める)。

また、VCXO30は、例えばLPF29の出力信号LPFoutの電圧値が大きい程、可変クロックV-CLKの周波数を上げる(つまり、位相を進める)。

また、上記R-ゲート26は、基準信号発生回路(SSG)を構成するFPGA31からのR-ゲート開閉制御信号Gateにより、リファレンスクロックR-CLKが位相比較器28へ入力される動作の開閉制御をする。

40

つまり、本実施例においては、リファレンスクロックR-CLKがPLL回路27の位相比較器28に入力される状態と、入力されない状態とを切り替えられるようにして、PLL回路27による周波数引込の動作を円滑ないしは速やかに行えるようにしている。

## 【0022】

これにより、最初に周波数引込の動作を開始させた場合、安定して周波数引込を行わせることができるようになると共に、仮に周波数引込が失敗、或いは引込が外れたような場合にも、R-ゲート26を閉にした後、開にしてPLL回路27による周波数引込の動作を再度、適切な状態で行えるようにしている。

50

なお、このR-ゲート開閉制御信号C<sub>gate</sub>は、図2(C)に示すように、例えば位相調整期間以外の期間で開閉(on/off)される。図2(C)のように例えばいくつかの位相調整期間ではR-ゲート開閉制御信号C<sub>gate</sub>が閉にされ(つまり、位相比較器28へのリファレンスクロックR-CLKを遮断)、PLL回路27はLPF29の出力信号LPFoutがグラウンド側に張り付いた状態に設定され、(後述のように)この状態でR-ゲート開閉制御信号C<sub>gate</sub>が開(位相比較器28ヘリファレンスクロックR-CLKを入力)にされることにより、実質的に周波数引込の動作を開始する。

#### 【0023】

上記LPF29の出力信号LPFoutは、同期検出回路(或いは引込検出回路)32に入力される。この同期検出回路32は、出力信号LPFoutのレベルからPLL回路27が位相同期、或いは周波数引込状態(lock)状態か、位相同期に失敗した引込していない状態(unlock)かの検出を行い、その検出信号をFPGA31に出力する。

FPGA31は、同期検出回路32からの検出信号を例えば内部に設けたカウンタ回路31aに入力して、発振器35のクロックを計数して位相同期した状態の時間をモニタする。

そして、(後述する図9に示す)所定時間t<sub>c</sub>を超えて位相同期していない状態が継続した場合には、このカウンタ回路31aの出力に基づいて、FPGA31は、R-ゲート開閉制御信号C<sub>gate</sub>を閉(off)にしてR-ゲート26を閉じた後、開(on)してリファレンスクロックR-CLKがPLL回路27の位相比較器28に入力される状態にする制御動作を行う。

#### 【0024】

このようにして、上記PLL回路27による周波数引込動作を再度行うことができるようしている。また、電源投入後における初期状態においても、FPGA31は、R-ゲート開閉制御信号C<sub>gate</sub>をoffにした後、onにする制御動作を行う。そして、周波数引込させ易いプロセスで周波数引込の動作を行う。

図4は同期検出回路32の構成例を示す。この同期検出回路32は、ウインドウ型コンパレータにより構成されている。第1のコンパレータ41の反転入力端には、例えば電源電圧Vddを抵抗R1、R2と抵抗R3で分割した電位VLが印加され、第2のコンパレータ42の非反転入力端には、電源電圧Vddを抵抗R1と抵抗R2、R3で分割した電位VHが印加される。

#### 【0025】

また、第1のコンパレータ41の非反転入力端及び第2のコンパレータ42の反転入力端には、LPF29の出力信号LPFoutが入力される。また、第1のコンパレータ41及び第2のコンパレータ42の出力信号はAND回路43に入力され、このアンド回路43から同期検出信号(或いは引込検出信号)lock/unlockを出力する。

つまり、図5に示すように、ウインドウ型コンパレータに入力されるLPF29の出力信号LPFoutのレベルが電位VLより低いと、ウインドウ型コンパレータは、"L"のunlockを出力する。また、LPF29の出力信号LPFoutのレベルが電位VHより高いと、ウインドウ型コンパレータは、同様に" L "のunlockを出力する。

#### 【0026】

一方、LPF29の出力信号LPFoutのレベルが電位VLからVH以内の間にあると、ウインドウ型コンパレータは、"H"の同期検出信号lockを出力する。

このようにして、同期検出回路32は、PLL回路27が引込状態にあるか否かの検出信号をFPGA31に出力する。そして、FPGA31は、この同期検出回路32の出力信号により、PLL回路27が同期状態にあるか否かをモニタし、所定時間t<sub>c</sub>を超えて同期していない状態が継続した場合には、再度周波数引込の動作を再開させる。

また、本実施例においては、位相調整期間において、PLL回路27による周波数引込の動作を開始させる場合、その動作を適切に行えるようにタイミング設定している。

10

20

30

40

50

このため、FPGA31は、PLL回路27による周波数引込の動作を開始させる動作制御信号としての間欠動作制御信号＼ENが位相比較器28に印加されるようにラッチ回路33に、制御信号Cenを出力する。この制御信号Cenは、図2(D)に示すように間欠的な位相調整期間をカバーするように出力される。

#### 【0027】

上記ラッチ回路33には、そのD入力端に制御信号Cenが印加され、またVCO30の可変クロックV-CLKが遅延回路(図1ではDLと略記)34により所定の遅延時間Taだけ遅延されてそのクロック入力端に印加される。

そして、位相調整期間になると、上記制御信号Cenが”H”となり、そのタイミング以降のVCO30から最初に出力される可変クロックV-CLKの立ち上がりエッジのタイミングから遅延回路34による遅延時間Taだけ遅延したタイミングで、ラッチ回路33の＼Q出力端から間欠動作制御信号＼ENが位相比較器28に印加され、位相比較器28は位相比較の動作を開始する。

つまり、PLL回路27が間欠的に周波数引込の動作を位相比較器28による位相比較の動作の制御により開始する場合、その間欠動作制御信号＼ENが位相比較器28に印加されるタイミングを遅延回路34及びラッチ回路33により設定する。そして、可変クロックV-CLKの立ち上がりエッジのタイミングに対して間欠動作制御信号＼ENが所定の時間以内で同期するようにタイミング設定している。このタイミング設定を図6を参照して説明する。

#### 【0028】

図6は可変クロックV-CLKの立ち上がりエッジのタイミングと間欠動作制御信号＼ENの立ち下がりエッジの同期タイミングの詳細を示す。図6において、例えば遅延回路34による遅延時間をXとした場合、X=0、X=T/2、X=Tの場合の間欠動作制御信号＼ENの立ち下がりエッジをそれぞれ実線、点線、1点鎖線で示す。

ここで、Xを設定する遅延回路34の入力は、図6の場合には、可変クロックV-CLKとしているが、可変クロックV-CLKの代わりにリファレンスクロックR-CLKとしても良い。

一般的に間欠動作型PLL回路においては、周波数引込と低位相雑音とを両立させようとした場合には、図6においてX=T/2の状態が最も望ましい最適条件になる。

#### 【0029】

これに対して、この最適条件からずれると、周波数引込を開始させた際のLPF29の出力信号LPFoutが電源電圧Vdd側或いはグラウンド側に張り付く傾向となってしまい、周波数引込特性が悪化する。

上記最適条件となるX=T/2の状態では、出力信号LPFoutがこれらの中間値に設定される傾向となり、入力されるリファレンスクロックがいずれの位相の場合にも速やかに追従させ易い状態となる。

最適条件から外れた場合、例えば、X<T/2とすると出力信号LPFoutが電源電圧Vdd側に張り付く傾向、また逆にX>T/2とすると、出力信号LPFoutがグラウンド側に張り付く傾向になる。

#### 【0030】

従って、非同期状態から周波数引込状態に速やかに遷移させるためには、位相雑音特性を犠牲にして広帯域ループ特性にしておくか、或いは位相雑音特性を確保するために低帯域ループ特性とし、望ましい周波数引込状態を得るために、上記のように間欠動作制御信号＼ENが立ち下がるタイミングとなる遅延時間Xを、かなり高い精度でX=T/2に設定する必要がある。

本実施例では、周波数引込後の動作を安定したものとするため、つまり低位相雑音特性を確保するために低帯域ループ特性にする。また、デバイスのばらつきや温度特性等の問題から上記X=T/2を高い精度で確保することは困難となるため、実用的なレベル内で同期タイミングの設定を行うようにする。

つまり、本実施例においては、遅延回路34による遅延時間をTaとした場合、図6に

10

20

30

40

50

示すように  $T / 4$   $T_a$   $T / 2$  程度に設定し、最適条件から緩和した条件設定としている。

#### 【0031】

この実用的なレベル内で同期タイミングの設定を行い、さらに上述したゲート手段により R - ゲート 26 を閉から開にする周波数引込プロセスにより、周波数引込を簡単な構成で円滑に行えるようにしている。

このように本実施例においては、PLL 回路 27 による間欠的に周波数引込の動作を開始させる場合のタイミング（間欠動作制御信号 \EN）と位相比較器 28 へのフィードバック信号である可変クロック V - CLK とを可変クロック V - CLK の周期よりも短い時間内で同期させるように同期タイミングの設定している。

このような構成にすることにより、LPF 29 を低位相雜音の低帯域ループ特性となるようにその定数を設定して、周波数引込を行う際には、実用的なレベルでの同期タイミングの設定と、ゲート手段によるゲート開閉で安定した周波数引込を行えるようにしている。

#### 【0032】

なお、FPGA 31 は、発振周波数の安定性が良好な水晶発振子を用いた発振器 35 により生成される基準クロックを用いて、上述した制御信号を生成すると共に、CCD 駆動回路 17 に対して、CCD 駆動信号を生成する際の基準となるタイミング信号を供給する。

次に本実施例の動作を説明する。図 1 に示すように内視鏡検査を行う場合、その内視鏡検査に適した挿入部長を有する電子内視鏡 2 を用い、この電子内視鏡 2 をビデオプロセッサ 3 に接続する。

そして、ビデオプロセッサ 3 の図示しない電源を投入する。するとビデオプロセッサ 3 の FPGA 31 は、動作状態となり CCD 駆動回路 17 に対して水平同期信号に同期したタイミング信号を送り、CCD 駆動回路 17 は、映像信号期間においては図 2 (A) に示すようにリセットパルス R を含む CCD 駆動信号を CCD 15 に出力する。

#### 【0033】

また、位相調整期間においては、CCD 駆動回路 17 は、例えばリセットパルス R のみを CCD 15 に出力する。

そして、CCD 15 は図 2 (B) に示す撮像信号を出力する。この場合、挿入部長やユニバーサルケーブル部 8 の長さに応じて、CCD 駆動回路 17 から出力されるリセットパルス R と、CCD 15 を経てビデオプロセッサ 3 に入力されるリセットパルス R とは図 2 (B) に示すようにケーブル長に応じて時間  $T_e$  の遅延ずれが発生する。

また、FPGA 31 は、例えば最初の位相調整期間の開始後よりも後のタイミングにおいて、図 2 (C) に示すように R - ゲート開閉制御信号 Cgate を off から on にする。そして、R - ゲート 26 を介してリファレンスクロック R - CLK が位相比較器 28 に入力される状態にする。

#### 【0034】

また、位相調整期間になると、FPGA 31 は、図 2 (D) に示すように制御信号 Cen を出力する。すると、図 7 (A) にも示すこの制御信号 Cen に対して、例えば可変クロック V - CLK が図 7 (B) のような状態の場合、遅延回路 34 の出力は、図 7 (C) のように可変クロック V - CLK に対して遅延回路 34 による遅延量に相当する所定時間  $T_a$  だけ遅れた波形となる。

そして、制御信号 Cen が "H" になった後における遅延回路 34 を通した出力信号が最初に立ち上がる立ち上がりエッジのタイミングでラッチ回路 33 から図 7 (D) に示す間欠動作制御信号 \EN が位相比較器 28 に印加される。

この間欠動作制御信号 \EN により位相比較器 28 は位相比較動作を開始する。

なお、図 7 (A) に示す制御信号 Cen は、(図 2 に示した位相調整期間) 毎に "H" となるために、図 7 (D) に示す間欠動作制御信号 \EN も、ほぼ位相調整期間に相当する期間  $T_{cap}$  每に "L" となる。

## 【0035】

図7(D)に示すように最初に間欠動作制御信号\ENが”L”になった時刻からそれが継続する期間Tcap、PLL回路27は、各水平期間毎に、周波数引込動作を行うことになる。なお、図7(D)に示す間欠動作制御信号\ENは、図7(A)の”L”の制御信号Cenを可変クロックV-CLKの立ち上がりエッジでラッチしたタイミングで”H”となる。

また、同期検出回路32においては、電源投入時は非同期状態であるため、\unlockを出力し、よってR-ゲート開閉制御信号Cgateは”L”となるため、R-ゲート26は閉じられた状態となっている。

## 【0036】

そして、間欠動作制御信号\ENが例えれば数回以上繰り返された後（この状態ではLPF29の出力信号LPFoutはグランド側のレベルに張り付く）、図2(C)の通りR-ゲート開閉制御信号Cgateはoffからonになる。

R-ゲート開閉制御信号Cgateがoffからonになる時刻をtoとした場合におけるPLL回路27による周波数引込の様子を図8に示す。

## 【0037】

間欠動作制御信号\ENが、最初に”L”となった場合における初期状態では、R-ゲート開閉制御信号Cgateは、まだoffであるため、リファレンスクロックR-CLKが位相比較器28へ入力されない状態である。

このため、LPF29の出力信号LPFoutは、位相比較器28の位相検出の結果を受けてグランド側に張り付いている。そして、リファレンスクロックR-CLKが時刻toで入力されると、図8に示すようにLPF29の出力信号LPFoutは、グラウンドレベルから電源電圧Vdd側に向かって上昇していく。

この場合、図6及び図7で説明したように可変クロックV-CLKに対して間欠動作制御信号\ENの立ち下がりタイミングがT/4-Ta-T/2程度で同期するように設定されている。

## 【0038】

以下は、何故LPF29の出力信号LPFoutが電源電圧Vddに向かって上昇していくのか、そして、最終的には位相同期が確定されるのか、についての解説である。

位相比較器28に入力される可変クロックV-CLKについて、非同期状態においてはどちらが先に位相比較器28に入力されるのか、その発生頻度を考えた場合、T/4-Ta-T/2であるが故に、リファレンスクロックR-CLKが可変クロックV-CLKに先行して（進み位相で）入力される場合の方が高くなる。このバイアス効果は、可変クロックV-CLKの位相を進めるべく、出力信号LPFoutを電源電圧Vddへ向かって遷移させる様、PLLループが動作する。

つまり、周波数引込範囲の近傍まではTaによるバイアス効果により出力信号LPFoutを遷移させ、その後、一般に言われるPLL回路のキャプチャプロセスに移行し位相同期が確定することとなる。

このようにして周波数引込が行われ、LPF29の出力信号LPFoutのレベルは位相同期した状態に保持される。

## 【0039】

また、このように位相同期した状態において、何らかの原因で位相同期状態から離脱した状態が発生した場合にも図9に示すように再び位相同期状態に設定する動作が行われる。

図9に示すように位相同期した状態から何らかの原因で位相同期が外れた状態になると、図9(A)に示すようにLPF29の出力信号LPFoutが例えれば電源電圧側のレベルへと変化する。

位相同期が外れた状態は、同期検出回路32によりモニタされている。そして、図9(B)に示すように位相同期が外れた状態が例えれば所定時間tc(tcは例えば200ms程度)以上継続すると、図9(C)に示すように(FPGA31は)R-ゲート開閉制御

10

20

30

40

50

信号 C<sub>gate</sub>を on から off にする。すると、位相比較器 28 には、リファレンスクロック R-CLK が入力されなくなるので、図 9 (A) に示すように LPF29 の出力信号 LPFout のレベルはグラウンドレベル側に向かって変化する。

#### 【0040】

そして、上記 R-ゲート開閉制御信号 C<sub>gate</sub>を off にした時間が例えば t<sub>off</sub> ( 例えは 200mS 程度 ) 以上経過すると、FPGA31 は、R-ゲート開閉制御信号 C<sub>gate</sub>を off から on にする ( 図 9 (C) 参照 )。すると、図 8 で説明したように LPF29 の出力信号 LPFout はグランドレベルから電源電圧 Vdd 側に向かって上昇し、その過程で周波数引込動作が円滑に行われる。

一方、上記の動作において、R-ゲート開閉制御信号 C<sub>gate</sub>を off から on にした場合、周波数引込に失敗する場合もあり得る。このため、FPGA31 は、この動作を同期検出回路 32 の出力によりモニタする。図 10 は、図 9 の動作を行った場合の、周波数引込に失敗した場合の動作を示す。

上記のように、FPGA31 は同期検出回路 32 の出力信号の状態をモニタする。そして、例えは図 10 に示すように R-ゲート開閉制御信号 C<sub>gate</sub>を off から on にした後、例えは所定時間 t<sub>d</sub> ( 例えは 200mS 程度 ) 経過しても同期していない状態 ( unlock 状態 ) が継続した場合には、FPGA31 は R-ゲート開閉制御信号 C<sub>gate</sub>を再び on から off にする。

#### 【0041】

そして、図 9 で説明したように FPGA31 は、時間 t<sub>off</sub> 後に R-ゲート開閉制御信号 C<sub>gate</sub>を off から on にして周波数引込を繰り返させる。

周波数引込が行われると、リファレンスクロック R-CLK に位相同期した可変クロック V-CLK が入力されるサンプリングパルス生成回路 23 は、映像信号期間における撮像信号をサンプリングするサンプリングパルス SP を CDS&A/D 回路 21 に出力し、撮像信号における信号部を、その信号部を抽出するタイミングで安定して抽出するようになる。

#### 【0042】

このように信号部を抽出するタイミングが安定して行われることにより、画質の良い内視鏡画像が得られる。

以上説明したように本実施例によれば、簡単な構成で、低位相雑音特性の低帯域ループ特性に設定した状態で周波数引込を円滑に行うことができる。また、低帯域ループ特性をキャプチャレンジとほぼ無関係に設定でき、位相比較周波数が高く、間欠動作の繰り返し周期が長い場合に非常に有効である。

また、簡単な構成で実現することができる。また、閉ループ応答を、低位相雑音特性の低帯域ループ特性に設定できるので、周波数引込後には安定した動作を確保でき、画質の良い内視鏡画像を継続して得ることができる。

#### 【実施例 2】

#### 【0043】

次に本発明の実施例 2 を図 11 を参照して説明する。図 11 は、本発明の実施例 2 を備えた内視鏡システム 1C を示す。この内視鏡システム 1C は、図 1 の内視鏡システム 1 において、電子内視鏡 2 に搭載された CCD15 とは画素数が異なる CCD15B を搭載して電子内視鏡 2B にも対応できるようにしている。図 11 では CCD15B を搭載した電子内視鏡 2B を示しているが、図 1 に示した電子内視鏡 2 にも対応できるビデオプロセッサ 3C を採用している。

このため、各電子内視鏡 2, 2B は、各電子内視鏡を識別すると共に、それに搭載された CCD の画素数を識別する ID 情報を発生する ID 部 51 を例えればコネクタ 9 に内蔵している。

また、本実施例におけるビデオプロセッサ 3C は、各 ID 部 51 の ID 情報を検出する ID 検出回路 52 を内蔵し、検出された ID 情報は FPGA31 に入力される。

#### 【0044】

10

20

30

40

50

また、図11に示すこのビデオプロセッサ3Cは、図1のビデオプロセッサ3において、さらにPLL回路27に分周回路53を備えたPLL回路27Cを採用している。この分周回路53はFPGA31により分周比が、CCD情報に含まれるCCDの画素数に応じて可変設定される。

また、FPGA31も、分周回路54を内蔵し、CCD15或いは15Bの画素数等の種別に応じた分周比で分周したタイミング信号をCCD駆動回路17に出力する。つまり、分周回路53、54は、実際に駆動されるCCDの画素数に応じてその分周比が同じ値が選択されるようになる。

また、FPGA31は、CCDの画素数に応じてリファレンスクロックR-CLK及び可変クロックV-CLKが変更されるのに伴い、遅延回路34における遅延の時間Taを切り替える。具体的には、例えば分周比と反比例した遅延の時間Taが選択設定される。画素数の変化があまり大きくな場合には、遅延の時間Taを切り替えることなく共通に使用しても良い。

#### 【0045】

なお、サンプリングパルス生成回路23は、必要に応じてCCDの画素数に応じて内部の遅延回路等による遅延量を切り替えるようにしても良い。

その他の構成は実施例1と同様の構成であり、同じ構成要素には同じ符号を付け、その説明を省略する。

本実施例によれば、CCDの画素数が異なる場合にも、その画素数のCCDを適切に駆動できるように分周回路54で分周したCCD駆動信号を発生し、これに対応して撮像信号に対する信号処理側もPLL回路27C内において分周回路53で可変クロックV-CLKを分周して位相比較器28により位相比較するようにしている。

従って、本実施例によれば、CCDの画素数が異なる場合にも、実施例1の場合と同様に無調整でそのCCDを内蔵した電子内視鏡に適切に対応できるようになる。その他、実施例1と同様の効果を有する。

#### 【0046】

以上説明した実施例1及び2においては、リファレンスクロックR-CLKのPLL回路27, 27C(の位相比較器28)への入力の開閉をリミッタアンプ25と位相比較器28との間に設けたR-ゲート26を用いて構成しているが、例えば図12に示す変形例のような構成にしても良い。

図12は実施例1に適用した変形例の内視鏡システム1Bの構成を示す。この内視鏡システム1Bにおけるビデオプロセッサ3Bは、図1のビデオプロセッサ3において、R-ゲート26に相当するゲート回路をFPGA31とCCD駆動回路17との間に配置した構成にしている。

具体的には、R-ゲート開閉制御信号Cgate及び間欠動作制御信号\ENはOR回路61に入力され、このOR回路61の出力信号はNAND回路62に入力される。このNAND回路62には実施例1の場合と同様にCCD駆動信号を発生するためにタイミング信号が入力され、このNAND回路62の出力はインバータ回路63を介してCCD駆動回路17に入力される。なお、NAND回路62の代わりにAND回路を用いてインバータ回路63を省いても良い。

#### 【0047】

その他の構成は実施例1と同様である。図12において、間欠動作制御信号\ENが"H"の期間、つまり位相調整期間付近を除外した映像信号期間においては、NAND回路62によるゲートは開となり、この映像信号期間においては実施例1と同様にCCD15は駆動される。

また、間欠動作制御信号\ENが"L"となる位相調整期間においては、FPGA31がR-ゲート開閉制御信号Cgateを出力するか否かによりFPGA31からCCD駆動回路17にタイミング信号(この場合にはリセットパルス)が出力されるか否かが決定される。そして、これにより、リセットパルスが、CCD15を経てリファレンスクロックR-CLKとして位相比較器28に入力されるか否かのゲート開閉が制御される。

10

20

30

40

50

本変形例では、ゲート手段は、各位相調整期間において C C D 駆動回路 17 へのリファレンスクロック R - C L K の入力の開閉を行う動作となる。そして、周波数引込などの動作は、実質的に実施例 1 と同様となる。そして、実施例 1 とほぼ同様の効果が得られる。

【付記】

1. 着脱自在に接続される内視鏡に内蔵された撮像素子から出力される基準クロックに対して、電圧制御発振回路で発生した可変クロックを位相比較器で位相比較するフェーズロックドループ回路を用いて、前記基準クロックに位相同期した可変クロックを生成する内視鏡用信号処理方法において、

前記フェーズロックドループ回路を、間欠的な期間、動作状態に設定する動作制御信号を発生する動作制御信号ステップと、

前記動作制御信号の出力開始時のタイミングを、前記可変クロックの出力タイミングと少なくとも前記可変クロックの周期よりも短い所定時間内で同期させる同期タイミング設定ステップと、

前記基準クロックの前記フェーズロックドループ回路への入力を少なくともゲート閉からゲート開にするゲート開閉制御ステップと、

を具備することを特徴とする内視鏡用信号処理方法。

【0048】

2. 付記 1 において、さらに前記可変クロックが前記基準クロックに位相同期している状態か否かを検出する同期検出ステップを有し、

前記同期検出ステップにより、前記可変クロックが前記基準クロックに位相同期していない時間が、所定時間を越えた場合には、前記ゲート開から一旦ゲート閉にした後、前記ゲート開閉制御ステップを行う。

【産業上の利用可能性】

【0049】

ケーブル長に基づく信号遅延量の補正をPLL回路を用いて自動的に調整する構成にすると共に、高画素に対応した高い周波数の場合にも低位相雑音特性に設定した状態で簡単に周波数引込を円滑に行うことができ、画質の良い内視鏡画像を得ることができる。

【図面の簡単な説明】

【0050】

【図 1】本発明の実施例 1 を備えた内視鏡システムの全体構成を示すブロック図。

【図 2】内視鏡を接続して駆動した場合におけるリセットパルス、撮像信号等を示すタイミングチャート。

【図 3】映像信号期間と位相調整期間の説明図。

【図 4】同期検出回路の構成例を示す回路図。

【図 5】図 4 の動作説明図。

【図 6】PLL回路における可変クロックと、位相比較器を動作状態に設定する間欠動作制御信号とを周波数引込させ易い所定のタイミングに同期させることの説明図。

【図 7】PLL動作させた場合の各部の出力を示すタイミングチャート。

【図 8】ゲート信号を off から on にして PLL回路を動作させた場合における周波数引込を行う様子を示す図。

【図 9】同期状態をモニタして、同期が外れた場合には一旦ゲート信号を off にした後、on にして周波数引込を行う様子を示す動作説明図。

【図 10】図 9 の動作の場合においてさらに周波数引込に失敗した場合の動作説明図。

【図 11】本発明の実施例 2 を備えた内視鏡システムの全体構成を示すブロック図。

【図 12】変形例を備えた内視鏡システムの全体構成を示すブロック図。

【符号の説明】

【0051】

1 ... 内視鏡システム

2 ... 電子内視鏡

3 ... ビデオプロセッサ

10

20

30

40

50

## 6 ... 挿入部

1 5 ... C C D

17...CCD 驅動回路

2 1 ... C D S & A / D 回路

2 6 ... R - ゲ - ト

2 7 ... P L L 回路

2 8 ... 位相比較器

2 9 .. L P F

3 0 .. v c x o

3 1 .. F P G A

### 3.2 同期檢出

### 3.3 ラッチ回路

3 4 遷延回路

卷之三

10

【 図 1 】

〔 四 2 〕

【図3】

【図4】

【図6】

【図5】

【図7】

【図8】

$0 > t_0 \quad R-CLK : off$  (ゲート手段: 閉)

$0 \leq t_0 \quad R-CLK : on$  (ゲート手段: 閉)

【図9】

【図10】

【図11】

【図12】

|                |                                                                                                                                                                                                                                                                                                                                           |         |            |

|----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|------------|

| 专利名称(译)        | 内窥镜的信号处理装置                                                                                                                                                                                                                                                                                                                                |         |            |

| 公开(公告)号        | <a href="#">JP2007159991A</a>                                                                                                                                                                                                                                                                                                             | 公开(公告)日 | 2007-06-28 |

| 申请号            | JP2005363695                                                                                                                                                                                                                                                                                                                              | 申请日     | 2005-12-16 |

| [标]申请(专利权)人(译) | 奥林巴斯医疗株式会社                                                                                                                                                                                                                                                                                                                                |         |            |

| 申请(专利权)人(译)    | オリンパスメディカルシステムズ株式会社                                                                                                                                                                                                                                                                                                                       |         |            |

| [标]发明人         | 高橋和正                                                                                                                                                                                                                                                                                                                                      |         |            |

| 发明人            | 高橋 和正                                                                                                                                                                                                                                                                                                                                     |         |            |

| IPC分类号         | A61B1/04 G02B23/24 H04N7/18                                                                                                                                                                                                                                                                                                               |         |            |

| CPC分类号         | H04N5/23203 A61B1/00006 A61B1/00105 A61B1/045 H04N2005/2255                                                                                                                                                                                                                                                                               |         |            |

| FI分类号          | A61B1/04.372 G02B23/24.A H04N7/18.M A61B1/00.640 A61B1/00.680 A61B1/045.610 A61B1/05                                                                                                                                                                                                                                                      |         |            |

| F-TERM分类号      | 2H040/CA04 2H040/CA11 2H040/CA23 2H040/GA02 2H040/GA06 2H040/GA11 4C061/AA00 4C061/BB01 4C061/CC06 4C061/DD00 4C061/JJ15 4C061/LL02 4C061/NN01 4C061/NN05 4C061/QQ02 4C061/SS05 5C054/CC07 5C054/EA03 5C054/EC06 5C054/HA12 4C161/AA00 4C161/BB01 4C161/CC06 4C161/DD00 4C161/JJ15 4C161/LL02 4C161/NN01 4C161/NN05 4C161/QQ02 4C161/SS05 |         |            |

| 代理人(译)         | 伊藤 进                                                                                                                                                                                                                                                                                                                                      |         |            |

| 其他公开文献         | JP4511454B2<br>JP2007159991A5                                                                                                                                                                                                                                                                                                             |         |            |

| 外部链接           | <a href="#">Espacenet</a>                                                                                                                                                                                                                                                                                                                 |         |            |

## 摘要(译)

解决的问题：提供一种内窥镜信号处理装置，该内窥镜信号处理装置使用能够在设定了低相位噪声特性的状态下以简单的结构进行频率引入的PLL电路。解决方案：R门26开启和关闭从CCD驱动电路17通过CCD 15输入到PLL电路27的参考时钟R-CLK。此外，延迟电路34延迟可变时钟V-CLK以延迟间歇操作控制信号EN的开始定时，以使相位比较器28能够在用于读取CCD 15的空像素的相位调节时段中进行操作。调整定时以使其与时钟V-CLK同步，并且将结果经由锁存电路33施加到相位比较器28。然后，通过从关闭到打开将R门26打开，在设置了低相位噪声特性的状态下以简单的配置执行频率引入。[选型图]图1